# VNA User Manual

September 20, 2020

# Contents

| Ι | Overview                    | 2 |

|---|-----------------------------|---|

|   | I.I USB                     | 2 |

|   | 1.2 RF ports                | 2 |

|   | I.3 LEDs                    | 2 |

|   | 1.4 Reference Output        | 3 |

|   | 1.5 Reference Input         | 3 |

| 2 | 2 Getting started           |   |

|   | 2.1 GUI elements types      | 4 |

|   | 2.2 Common GUI elements     | 4 |

| 3 | Operating Modes             | 6 |

|   | 3.1 Vector Network Analyzer | 6 |

|   | 3.2 Signal Generator        | 6 |

|   | 3.3 Spectrum Analyzer       | 6 |

| 4 | Troubleshooting             | 6 |

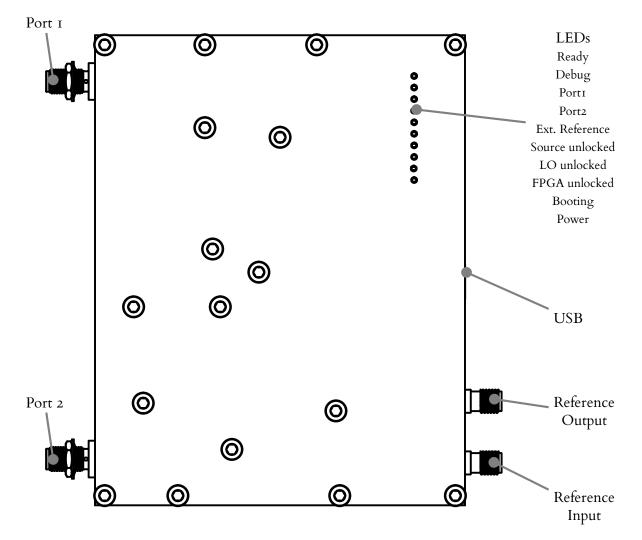

### 1 Overview

#### I.I USB

The VNA uses a USB-C connector as the power supply and for data transmission. The hardware supports the USB power delivery standard<sup>1</sup>, requires 5 V and draws up to 1.2 A of current.

The implemented USB device is limited to USB 2.0 Fullspeed and data transmission will work with any USB 2.0 or 3.0 port (no USB-C required). However, the current consumption exceeds the specifications for USB 2.0 and 3.0 ports and the VNA may be unable to fully boot when the USB host limits the current.

#### 1.2 RF ports

RF connector to connect the DUT. Both ports are identical and the device architecture support full S-Parameter measurements (S11, S21, S12 and S22).

The RF ports have no input protection, do not apply a signal with more than +10 dBm of power.

#### 1.3 LEDs

Ten LEDs indicate the status:

<sup>&</sup>lt;sup>1</sup>Work in progress, the device will not negotiate USB-PD yet

Ready (green) Indicates fully booted VNA, ready to take measurements

Debug (green) Not used at the moment

Port 1 (green) Active output signal on port 1

Port 2 (green) Active output signal on port 2

Ext. Reference (green) External reference in use

**Source unlocked (red)** The source PLL failed to lock (it may turn on briefly during a sweep, this is not a problem)

**LO unlocked (red)** The 1.LO PLL failed to lock (it may turn on briefly during a sweep, this is not a problem)

FPGA unlocked (red) The FPGA clock PLL failed to lock

Booting (red) Indicates boot process, also used for error codes

Power (green) USB power valid

### 1.4 Reference Output

Optional reference output port (user selectable 10 MHz or 100 MHz). The output power is approximately +3 dBm.

### 1.5 Reference Input

1

High impedance reference input port. When applying a  $10\,\rm MHz$  input signal, it can be used to overwrite the internal TCXO.

Due to the high impedance input, the external input may detect a valid signal when picking up external radiation. If this is a problem, either terminate the reference input connector or disable automatic reference switching.

# 2 Getting started

- 1. Connect the VNA to a computer using the USB port. After a couple of seconds, only the "Power" and "Ready" LEDs should stay on. If the "Ready" LED does not turn on or the "Booting" LED indicates an error code, there is a problem und the device will not function properly. See section 4 for possible solutions.

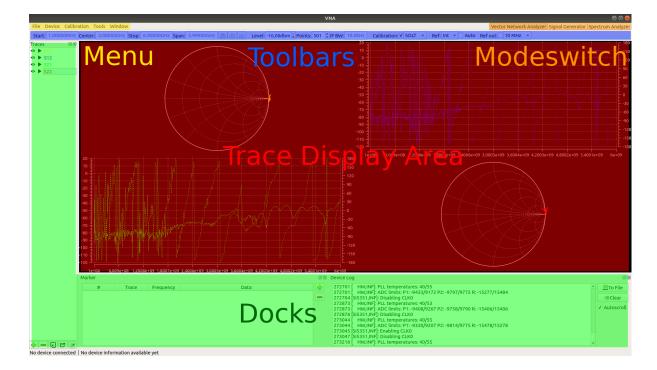

- 2. Start the PC application to connect to the VNA. The window should look similar to this:

# 2.1 GUI elements types

The VNA application is made up of six areas containing different types of control:

- The Trace Display Area shows the measured data in various diagrams.

- The Toolbars provide access to commonly used device settings.

- The Menu at the top left handles less common settings or more complex actions (often with additional popup windows).

- The Docks mostly provide access to display related settings such as traces and markers.

- The **Statusbar** at the bottom show some basic informations about the connected device.

- The **Modeswitch** at the top right allows changing the VNA operating mode. Although it is primarily designed as a vector network analyzer, the hardware architecture allow some other operating modes with certain limitations.

Depending on the current operating mode, the available toolbars, docks and menu entries change. It is also possible to rearrange the docks and toolbars.

#### 2.2 Common GUI elements

Certain control elements are always available, regardless of the selected mode. They control settings of the VNA that are not specific to any of the operating modes.

#### 2.2.1 Reference Toolbar

The reference toolbar controls the external reference output as well as the input.

```

Ref: Int 👻 🗌 Auto Ref out: 🗌 10 MHz 💌

```

The reference can be set to "Int" (internal TCXO), "Ext" (external 10 MHz signal) or to automatic mode. In automatic mode, the reference will switch to the external input when a signal is detected, otherwise it will use the internal TCXO.

The external reference output may either be disabled or set to 10 MHz or 100 MHz.

#### 2.2.2 Device Log Dock

This dock shows the debug output of the VNA (the same messages as on the internal UART port). It may help to identify problems, otherwise it is not required for operation.

| Device Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 8       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 272701 [ HW,INF]: PLL temperatures: 40/55<br>272701 [ HW,INF]: ADC limits: P1: -9433/9172 P2: -9797/9772 R: -15277/15484<br>272704 [SI5351,INF]: Disabling CLK0<br>272873 [ HW,INF]: PLL temperatures: 40/53<br>272873 [ HW,INF]: ADC limits: P1: -9408/9267 P2: -9758/9790 R: -15406/15406<br>272876 [SI5351,INF]: Disabling CLK0<br>273044 [ HW,INF]: PLL temperatures: 40/55<br>273044 [ HW,INF]: ADC limits: P1: -9330/9207 P2: -9814/9775 R: -15478/15278<br>273045 [SI5351,INF]: Enabling CLK0<br>273047 [ SI5351,INF]: Enabling CLK0<br>273047 [ SI5351,INF]: Disabling CLK0<br>273047 [ SI5351,INF]: PLL temperatures: 40/55 | ▲ To File |

#### 2.2.3 Device Menu

The device menu controls the connection state, allows low level hardware access and to perform firmware updates:

- Update Device List: Scans the USB port for connected devices. Clicking this action simply updates the list of devices, no connection is established.

- Connect to: Select which VNA to connect to. Different devices are identified by their serial number.

- Disconnect: Disconnect from the VNA.

- Manual Control: Starts the manual control dialog in which all hardware settings are accessible (mostly used for testing purposes):

| Manual System Control 😵                                                                                                                                 |                                                                          |                                                                                                                                       |                                                                                                                                                                            |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal Generation                                                                                                                                       |                                                                          |                                                                                                                                       | Measurements                                                                                                                                                               |  |  |  |

| Highband Source                                                                                                                                         | Lowband Source                                                           | Attenuator                                                                                                                            | Port 1                                                                                                                                                                     |  |  |  |

| <ul> <li>Chip Enable</li> <li>RF Enable</li> <li>✓ Locked</li> <li>Power: -4dbm ▼</li> <li>Frequency: 1.00000GHz</li> <li>Lowpass: 947MHz ▼</li> </ul>  | Enable Power: 2mA Frequency: 1.00000MH2 Source Switch Lowband • Highband | z 0,00db +<br>Amplifier<br>Enable<br>Port Switch<br>• Port 1<br>• Port 2                                                              | ADC min: -1<br>ADC max: 3<br>Magnitude: 3.46238<br>Phase: -143.675<br>Referenced: -0.7db@21°<br>Port 2<br>ADC min: 7                                                       |  |  |  |

| Signal Analysis                                                                                                                                         |                                                                          | ADC max: 11                                                                                                                           |                                                                                                                                                                            |  |  |  |

| LO1 L                                                                                                                                                   | 02                                                                       | Aquisition                                                                                                                            | Magnitude: 8.0964                                                                                                                                                          |  |  |  |

| <ul> <li>Chip Enable</li> <li>RF Enable</li> <li>✓ Locked</li> <li>Freq. Type: IF1 ▼</li> <li>Frequency: 1.06000GHz</li> <li>IF1: 60.0000MHz</li> </ul> | Enable Freq. Type: IF2 Frequency: 60.2500MHz IF2: 250.000kHz             | <ul> <li>Port 1 Enable</li> <li>Port 2 Enable</li> <li>Reference Enable</li> <li>Samples: 130944 +</li> <li>Window: None +</li> </ul> | Phase:       -138.137         Referenced:       6.7db@27°         ADC min:       3         ADC max:       6         Magnitude:       3.73212         Phase:       -164.929 |  |  |  |

• Firmware Update: Load a new microcontroller firmware and FPGA configuration into the VNA. Do not disconnect power while updating the firmware!

| Firmware Update 😣                                                                                                                                       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| File: //home/jan/Projekte/VNA2/test.vnafw                                                                                                               |  |  |  |  |

| Evaluating file<br>Erasing device memory<br>Transferring firmware<br>Triggering device update<br>Rebooting device<br>device enumerated, update complete |  |  |  |  |

| 100%                                                                                                                                                    |  |  |  |  |

| ►Start                                                                                                                                                  |  |  |  |  |

### 2.2.4 Window Menu

The window menu allows hiding not needed toolbars and docks. It also contains some application preferences.

# 3 Operating Modes

# 3.1 Vector Network Analyzer

In this operating mode, the VNA takes S-parameter measurements. A source signal is generated and alternately applied to the RF ports. The incoming signal at both RF ports is measured, resulting in the four S-parameters S11 and S21 (when the source signal is routed to port 1) as well as S12 and S22 (when it is routed to port 2).

# 3.2 Signal Generator

# 3.3 Spectrum Analyzer

# 4 Troubleshooting

If the was an error in the boot process, the "Booting" LED will blink an error code repeatedly:

| Error<br>Code | Meaning                        | Possible solution                                                               |

|---------------|--------------------------------|---------------------------------------------------------------------------------|

| Ι             | Failed to detect FLASH memory  |                                                                                 |

| 2             | Invalid FLASH content          | Perform firmware update                                                         |

| 3             | Failed to configure FPGA       | Check FPGA bitstream generator settings                                         |

| 4             | Hardware initialization failed | Verify that FPGA bitstream and uC<br>firmware are created from the same release |